clk_div_n Entity Reference

Clock divider entity. More...

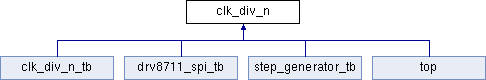

Inheritance diagram for clk_div_n:

Entities | |

| rtl | architecture |

| Architecture rtl of clk_div_n entity. More... | |

Libraries | |

| ieee | |

| Using IEEE library. | |

Use Clauses | |

| std_logic_1164 | |

| Using IEEE standard logic components. | |

| numeric_std | |

| Using IEE standard numeric components. | |

Generics | |

| clk_div | integer range 2 TO integer ' high := 4 |

| Divider amount. | |

Ports | |

| clk_in | in std_logic |

| Clock. | |

| rst_in | in std_logic |

| Asynchronous reset. | |

| div_clr_in | in std_logic |

| Divider clear flag. | |

| div_adv_in | in std_logic |

| Divider advance flag. | |

| div_end_out | out std_logic |

| Divider end flag. | |

| div_pls_out | out std_logic |

| Divider pulse flag. | |

Detailed Description

Clock divider entity.

This clock divider takes an input clock and divides it by an integer value.

Definition at line 19 of file clk_div_n.vhd.

The documentation for this class was generated from the following file:

- fpga/common/utility/source/clk_div_n.vhd