#include <HFRiscV.hpp>

Public Member Functions | |

| void | dumpregs () |

| void | bp (risc_v_state *s, uint32_t ir) |

| int32_t | mem_read (risc_v_state *s, int32_t size, uint32_t address) |

| Reads data from the memory. More... | |

| void | mem_write (risc_v_state *s, int32_t size, uint32_t address, uint32_t value) |

| Reads data from memory. More... | |

| HFRiscV (std::string name, Signal< uint8_t > *intr, Signal< uint8_t > *stall, Memory *mem) | |

| ~HFRiscV () | |

| Signal< uint8_t > * | GetSignalStall () |

| Signal< uint8_t > * | GetSignalIntr () |

| SimulationTime | Run () |

| Run method from the base TimedModel class, overloaded. More... | |

| void | Reset () |

| ProcessorState< uint32_t > * | GetState () |

| This method returns the state model of the processor. More... | |

| Memory * | GetMemory () |

| This method returns a pointer to the object that models the memory core. More... | |

Public Attributes | |

| std::ofstream | output_debug |

| std::ofstream | output_uart |

Private Attributes | |

| uint32_t | _last_pc |

| Signal< uint8_t > * | _signal_intr |

| Signal< uint8_t > * | _signal_stall |

| risc_v_state * | s |

| int | i |

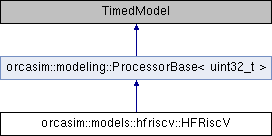

Detailed Description

Definition at line 76 of file HFRiscV.hpp.

Constructor & Destructor Documentation

§ HFRiscV()

| HFRiscV::HFRiscV | ( | std::string | name, |

| Signal< uint8_t > * | intr, | ||

| Signal< uint8_t > * | stall, | ||

| Memory * | mem | ||

| ) |

Definition at line 738 of file HFRiscV.cpp.

§ ~HFRiscV()

| HFRiscV::~HFRiscV | ( | ) |

Definition at line 789 of file HFRiscV.cpp.

Member Function Documentation

§ bp()

| void HFRiscV::bp | ( | risc_v_state * | s, |

| uint32_t | ir | ||

| ) |

Definition at line 53 of file HFRiscV.cpp.

§ dumpregs()

| void HFRiscV::dumpregs | ( | ) |

Definition at line 44 of file HFRiscV.cpp.

§ GetMemory()

|

inlineinherited |

This method returns a pointer to the object that models the memory core.

It is made private to avoid being changed by the processor core implementation.

- Returns

- a pointers to the memory model

Definition at line 86 of file ProcessorBase.cpp.

§ GetSignalIntr()

| Signal< uint8_t > * HFRiscV::GetSignalIntr | ( | ) |

Definition at line 157 of file HFRiscV.cpp.

§ GetSignalStall()

| Signal< uint8_t > * HFRiscV::GetSignalStall | ( | ) |

Definition at line 153 of file HFRiscV.cpp.

§ GetState()

|

inlineinherited |

This method returns the state model of the processor.

Access the current state of the processor.

This is ideally used from the top level simulator to report processor states at the end of simulation.

- Returns

- a pointer to the processor state struct.

- A pointer to the state of the processor.

Definition at line 81 of file ProcessorBase.cpp.

§ mem_read()

| int32_t HFRiscV::mem_read | ( | risc_v_state * | s, |

| int32_t | size, | ||

| uint32_t | address | ||

| ) |

Reads data from the memory.

- Parameters

-

s Current state of the core size Size of data to be read. Must be 32, 16, or 8. address Starting address to read from

- Returns

- Data read

Definition at line 71 of file HFRiscV.cpp.

§ mem_write()

| void HFRiscV::mem_write | ( | risc_v_state * | s, |

| int32_t | size, | ||

| uint32_t | address, | ||

| uint32_t | value | ||

| ) |

Reads data from memory.

- Parameters

-

s The current state of the processor size Size of data to be read. Must be 32, 16 or 8. address Starting address of data value Value to be written to the address

Definition at line 168 of file HFRiscV.cpp.

§ Reset()

| void HFRiscV::Reset | ( | ) |

Definition at line 806 of file HFRiscV.cpp.

§ Run()

|

virtual |

Run method from the base TimedModel class, overloaded.

We include in the overloading external components that would apply to all processors. Examples include energy estimation (through counters) and GDBRSP.

- Returns

- the number of cycles to skip until next schedule.

Implements orcasim::modeling::ProcessorBase< uint32_t >.

Definition at line 368 of file HFRiscV.cpp.

Member Data Documentation

§ _last_pc

|

private |

Definition at line 78 of file HFRiscV.hpp.

§ _signal_intr

|

private |

Definition at line 81 of file HFRiscV.hpp.

§ _signal_stall

|

private |

Definition at line 82 of file HFRiscV.hpp.

§ i

|

private |

Definition at line 87 of file HFRiscV.hpp.

§ output_debug

| std::ofstream orcasim::models::hfriscv::HFRiscV::output_debug |

Definition at line 137 of file HFRiscV.hpp.

§ output_uart

| std::ofstream orcasim::models::hfriscv::HFRiscV::output_uart |

Definition at line 138 of file HFRiscV.hpp.

§ s

|

private |

Definition at line 85 of file HFRiscV.hpp.

The documentation for this class was generated from the following files:

- models/hfriscv-core/include/HFRiscV.hpp

- models/hfriscv-core/src/HFRiscV.cpp

1.8.12

1.8.12