#include <DmaNetif.hpp>

Public Member Functions | |

| DmaNetifRecvState | GetRecvState () |

| DmaNetifSendState | GetSendState () |

| Signal< uint8_t > * | GetSignalStall () |

| Signal< uint8_t > * | GetSignalIntr () |

| Signal< uint8_t > * | GetSignalProgSend () |

| Signal< uint8_t > * | GetSignalProgRecv () |

| Signal< uint8_t > * | GetSignalRecvReload () |

| Signal< uint8_t > * | GetSignalSendStatus () |

| Signal< uint32_t > * | GetSignalRecvStatus () |

| Signal< uint32_t > * | GetSignalProgAddr () |

| Signal< uint32_t > * | GetSignalProgSize () |

| Signal< uint16_t > * | GetSignalProgDest () |

| void | SetSignalStall (Signal< uint8_t > *) |

| void | SetSignalIntr (Signal< uint8_t > *) |

| void | SetSignalSendStatus (Signal< uint8_t > *) |

| void | SetSignalProgSend (Signal< uint8_t > *) |

| void | SetSignalProgRecv (Signal< uint8_t > *) |

| void | SetSignalRecvReload (Signal< uint8_t > *) |

| void | SetSignalRecvStatus (Signal< uint32_t > *) |

| void | SetSignalProgAddr (Signal< uint32_t > *) |

| void | SetSignalProgSize (Signal< uint32_t > *) |

| void | SetSignalProgDest (Signal< uint16_t > *) |

| void | sendProcess () |

| void | recvProcess () |

| SimulationTime | Run () |

| Method which is called by the simulator when during the execution of the TimedModel. More... | |

| void | Reset () |

| Resets the instance to its starting state. More... | |

| void | SetMem0 (Memory *) |

| void | SetMem1 (Memory *) |

| void | SetMem2 (Memory *) |

| void | SetOutputBuffer (Buffer< FlitType > *ob) |

| Buffer< FlitType > * | GetInputBuffer () |

| DmaNetif (std::string name) | |

| ~DmaNetif () | |

a name that identifies the model, advisably not empty. | |

Default ctor. | |

| std::string | GetName () |

| Getter method for the <_name> field. More... | |

| void | SetName (std::string s) |

| Setter method for the <_name> field. More... | |

Private Attributes | |

| Memory * | _mem0 |

| Memory * | _mem1 |

| Memory * | _mem2 |

| DmaNetifRecvState | _recv_state |

| DmaNetifSendState | _send_state |

| FlitType | _recv_reg |

| FlitType | _send_reg |

| Signal< uint8_t > * | _sig_stall |

| Signal< uint8_t > * | _sig_intr |

| Signal< uint8_t > * | _sig_recv_reload |

| Signal< uint8_t > * | _sig_prog_send |

| Signal< uint8_t > * | _sig_prog_recv |

| Signal< uint8_t > * | _sig_send_status |

| Signal< uint32_t > * | _sig_recv_status |

| Signal< uint32_t > * | _sig_prog_addr |

| Signal< uint32_t > * | _sig_prog_size |

| Signal< uint16_t > * | _sig_prog_dest |

| uint32_t | _recv_payload_size |

| uint32_t | _recv_payload_remaining |

| uint32_t | _recv_address |

| uint32_t | _send_payload_size |

| uint32_t | _send_payload_remaining |

| uint32_t | _send_address |

| Buffer< FlitType > * | _ib |

| Buffer< FlitType > * | _ob |

Detailed Description

- Date

- 10/03/18

Definition at line 98 of file DmaNetif.hpp.

Constructor & Destructor Documentation

§ DmaNetif()

|

explicit |

Definition at line 43 of file DmaNetif.cpp.

§ ~DmaNetif()

| DmaNetif::~DmaNetif | ( | ) |

Definition at line 63 of file DmaNetif.cpp.

Member Function Documentation

§ GetInputBuffer()

Definition at line 76 of file DmaNetif.cpp.

§ GetName()

|

inherited |

§ GetRecvState()

| DmaNetifRecvState DmaNetif::GetRecvState | ( | ) |

Definition at line 81 of file DmaNetif.cpp.

§ GetSendState()

| DmaNetifSendState DmaNetif::GetSendState | ( | ) |

Definition at line 82 of file DmaNetif.cpp.

§ GetSignalIntr()

| Signal< uint8_t > * DmaNetif::GetSignalIntr | ( | ) |

Definition at line 90 of file DmaNetif.cpp.

§ GetSignalProgAddr()

| Signal< uint32_t > * DmaNetif::GetSignalProgAddr | ( | ) |

Definition at line 97 of file DmaNetif.cpp.

§ GetSignalProgDest()

| Signal< uint16_t > * DmaNetif::GetSignalProgDest | ( | ) |

Definition at line 100 of file DmaNetif.cpp.

§ GetSignalProgRecv()

| Signal< uint8_t > * DmaNetif::GetSignalProgRecv | ( | ) |

Definition at line 93 of file DmaNetif.cpp.

§ GetSignalProgSend()

| Signal< uint8_t > * DmaNetif::GetSignalProgSend | ( | ) |

Definition at line 92 of file DmaNetif.cpp.

§ GetSignalProgSize()

| Signal< uint32_t > * DmaNetif::GetSignalProgSize | ( | ) |

Definition at line 98 of file DmaNetif.cpp.

§ GetSignalRecvReload()

| Signal< uint8_t > * DmaNetif::GetSignalRecvReload | ( | ) |

Definition at line 94 of file DmaNetif.cpp.

§ GetSignalRecvStatus()

| Signal< uint32_t > * DmaNetif::GetSignalRecvStatus | ( | ) |

Definition at line 96 of file DmaNetif.cpp.

§ GetSignalSendStatus()

| Signal< uint8_t > * DmaNetif::GetSignalSendStatus | ( | ) |

Definition at line 91 of file DmaNetif.cpp.

§ GetSignalStall()

| Signal< uint8_t > * DmaNetif::GetSignalStall | ( | ) |

Definition at line 89 of file DmaNetif.cpp.

§ recvProcess()

| void DmaNetif::recvProcess | ( | ) |

Definition at line 124 of file DmaNetif.cpp.

§ Reset()

|

virtual |

Resets the instance to its starting state.

Must be implemented by subclasses

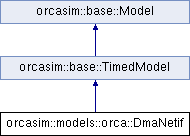

Implements orcasim::base::TimedModel.

Definition at line 67 of file DmaNetif.cpp.

§ Run()

|

virtual |

Method which is called by the simulator when during the execution of the TimedModel.

Must be implemented by subclasses.

Implements orcasim::base::TimedModel.

Definition at line 116 of file DmaNetif.cpp.

§ sendProcess()

| void DmaNetif::sendProcess | ( | ) |

Definition at line 348 of file DmaNetif.cpp.

§ SetMem0()

| void DmaNetif::SetMem0 | ( | Memory * | m0 | ) |

Definition at line 84 of file DmaNetif.cpp.

§ SetMem1()

| void DmaNetif::SetMem1 | ( | Memory * | m1 | ) |

Definition at line 85 of file DmaNetif.cpp.

§ SetMem2()

| void DmaNetif::SetMem2 | ( | Memory * | m2 | ) |

Definition at line 86 of file DmaNetif.cpp.

§ SetName()

|

inherited |

§ SetOutputBuffer()

Definition at line 72 of file DmaNetif.cpp.

§ SetSignalIntr()

| void DmaNetif::SetSignalIntr | ( | Signal< uint8_t > * | c | ) |

Definition at line 104 of file DmaNetif.cpp.

§ SetSignalProgAddr()

| void DmaNetif::SetSignalProgAddr | ( | Signal< uint32_t > * | c | ) |

Definition at line 111 of file DmaNetif.cpp.

§ SetSignalProgDest()

| void DmaNetif::SetSignalProgDest | ( | Signal< uint16_t > * | c | ) |

Definition at line 114 of file DmaNetif.cpp.

§ SetSignalProgRecv()

| void DmaNetif::SetSignalProgRecv | ( | Signal< uint8_t > * | c | ) |

Definition at line 107 of file DmaNetif.cpp.

§ SetSignalProgSend()

| void DmaNetif::SetSignalProgSend | ( | Signal< uint8_t > * | c | ) |

Definition at line 106 of file DmaNetif.cpp.

§ SetSignalProgSize()

| void DmaNetif::SetSignalProgSize | ( | Signal< uint32_t > * | c | ) |

Definition at line 112 of file DmaNetif.cpp.

§ SetSignalRecvReload()

| void DmaNetif::SetSignalRecvReload | ( | Signal< uint8_t > * | c | ) |

Definition at line 108 of file DmaNetif.cpp.

§ SetSignalRecvStatus()

| void DmaNetif::SetSignalRecvStatus | ( | Signal< uint32_t > * | c | ) |

Definition at line 110 of file DmaNetif.cpp.

§ SetSignalSendStatus()

| void DmaNetif::SetSignalSendStatus | ( | Signal< uint8_t > * | c | ) |

Definition at line 105 of file DmaNetif.cpp.

§ SetSignalStall()

| void DmaNetif::SetSignalStall | ( | Signal< uint8_t > * | c | ) |

Definition at line 103 of file DmaNetif.cpp.

Member Data Documentation

§ _ib

Definition at line 138 of file DmaNetif.hpp.

§ _mem0

|

private |

Definition at line 101 of file DmaNetif.hpp.

§ _mem1

|

private |

Definition at line 102 of file DmaNetif.hpp.

§ _mem2

|

private |

Definition at line 103 of file DmaNetif.hpp.

§ _ob

Definition at line 139 of file DmaNetif.hpp.

§ _recv_address

|

private |

Definition at line 130 of file DmaNetif.hpp.

§ _recv_payload_remaining

|

private |

Definition at line 129 of file DmaNetif.hpp.

§ _recv_payload_size

|

private |

Definition at line 128 of file DmaNetif.hpp.

§ _recv_reg

|

private |

Definition at line 110 of file DmaNetif.hpp.

§ _recv_state

|

private |

Definition at line 106 of file DmaNetif.hpp.

§ _send_address

|

private |

Definition at line 135 of file DmaNetif.hpp.

§ _send_payload_remaining

|

private |

Definition at line 134 of file DmaNetif.hpp.

§ _send_payload_size

|

private |

Definition at line 133 of file DmaNetif.hpp.

§ _send_reg

|

private |

Definition at line 111 of file DmaNetif.hpp.

§ _send_state

|

private |

Definition at line 107 of file DmaNetif.hpp.

§ _sig_intr

|

private |

Definition at line 115 of file DmaNetif.hpp.

§ _sig_prog_addr

|

private |

Definition at line 122 of file DmaNetif.hpp.

§ _sig_prog_dest

|

private |

Definition at line 125 of file DmaNetif.hpp.

§ _sig_prog_recv

|

private |

Definition at line 118 of file DmaNetif.hpp.

§ _sig_prog_send

|

private |

Definition at line 117 of file DmaNetif.hpp.

§ _sig_prog_size

|

private |

Definition at line 123 of file DmaNetif.hpp.

§ _sig_recv_reload

|

private |

Definition at line 116 of file DmaNetif.hpp.

§ _sig_recv_status

|

private |

Definition at line 121 of file DmaNetif.hpp.

§ _sig_send_status

|

private |

Definition at line 119 of file DmaNetif.hpp.

§ _sig_stall

|

private |

Definition at line 114 of file DmaNetif.hpp.

The documentation for this class was generated from the following files:

- models/orca-network-interface/include/DmaNetif.hpp

- models/orca-network-interface/src/DmaNetif.cpp

1.8.12

1.8.12